Stm32f4 Hal Disable Interrupt Gpio

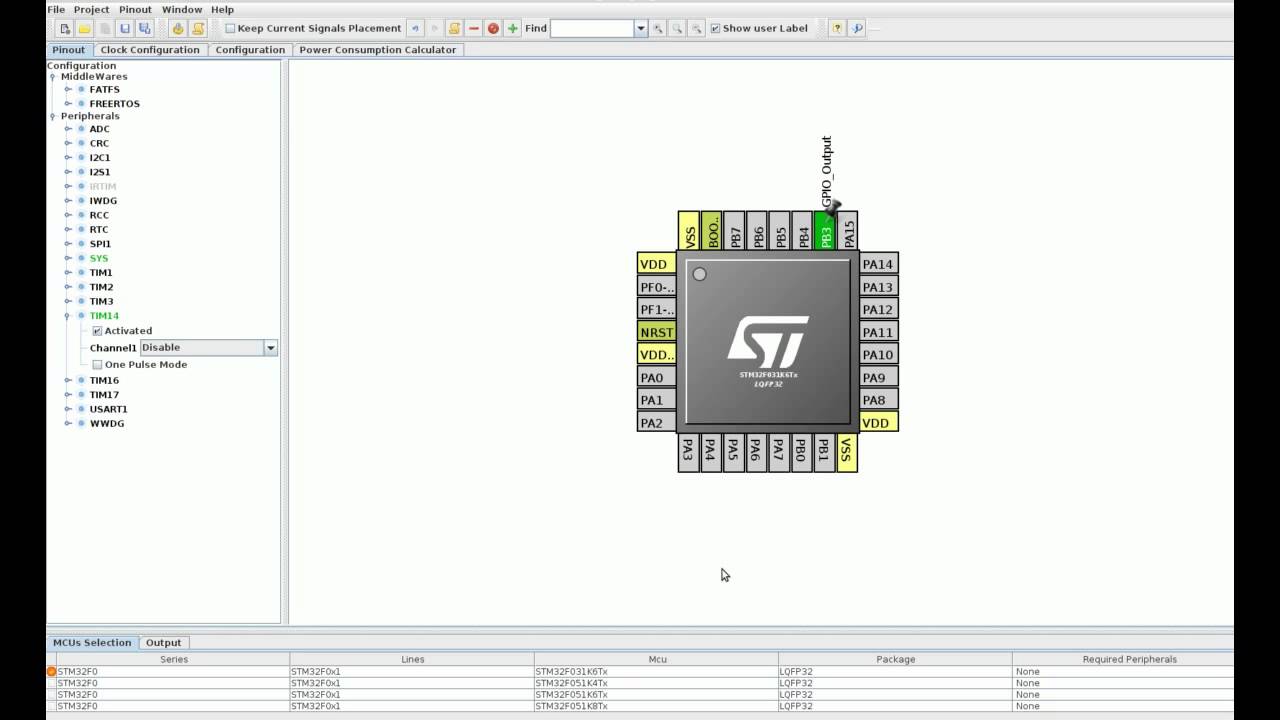

One of my major gripes with the STM32 family is the documentation. Thereference manual is pretty comprehensive but is not well organized. Asimple task of figuring out how to use external interrupts is utterlyunclear. The availability of the peripheral libraries which again arenot well documented exacerbates this problem. Programmers are encouragedto recycle peripheral library based code from the available exampleswithout really understanding the hardware.they simply use the codebecause they know it works. This approach might seem reasonable but whentrying to implement a complicated peripheral setup it can cause muchangst.Now that I've got my rant out of the way, let's take a look atinterrupts on the STM32F0 chip and specifically external Interrupts. STM32F0 Interrupt vector TableThe STM32F0 Microcontroller is based on the Cortex-M0 core and possessesan NVIC (nested vector interrupt control ) peripheral which can keeptrack of up to 32 interrupt vectors shown in Figure 1 includingexceptions.

Stm32f4 Hal Disable Interrupt Gpio Server

Each one of these interrupt vectors can be mapped to a setof related interrupt sources. For example all USART1 interrupt eventssuch as: Transmission Complete, Clear to Send, Transmit Data Registerempty or Framing error (in Smartcard mode),Overrun error, Receive dataregister not empty, Character match e.t.c are mapped to the USART1interrupt vector no# 27.Similarly external interrupt lines 0 & 1 are mapped to interrupt vector5, external interrupt lines 2 & 3 are mapped to interrupt vector 6 andexternal interrupt lines 4 through 15 are mapped to interrupt vector 7. Mapping Pins to External interrupt linesThe GPIO pins are mapped to the various external interrupt lines by wayof multiplexers as shown in Figure 2. For each external interrupt line,up to 6 pins can be mapped. The mapping is accomplished by the EXTIXXbits in the SYSCFGEXTICRX registers.To configure an external interrupt one must configure the externalinterrupt (EXTI) peripheral as well as the NVIC peripheral. The generalprocedure is as follows:.

Configure the EXTIXX bits in the SYSCFGEXTICRX registers to map theGPIO pin(s) of interest to the appropriate external interrupt lines(EXTI0-EXTI15). For the external interrupt lines (EXTIXX) of interest choose a signalchange that will trigger the external interrupt.The signal change canbe a rising edge, a falling edge or both. These can be set via theEXTIRTSR (rising) and the EXTIFTSR (falling) registers. Unmask the external interrupt line(s) of interest. By setting thebit corresponding to the EXTI line of interest in the EXTIMRregister.

Set the priority for the interrupt vector in question in the NVICeither via the CMSIS based 'NVICSetPriority' function or throughthe IPR0-IPR7 registers. Enable the interrupt in the NVIC either via the CMSIS based'NVICEnableIRQ' function or via the ISER register. Write your interrupt service routine (ISR). Inside your interrupt service routine, check the source of theinterrupt.either the GPIO pin directly or the external interruptline.

Once you figure out which one triggered the interrupt, performthe interrupt processing scheme associated with it. Make sure thatyou clear the corresponding pending bit of the external interruptlines of interest in the EXTPR (external interrupt pendingregister) register by writing a '1' to it.An example can be found in the project described in the previous blog entry;.In that example we waited (polling) for a button press on pin PA0 toadvance a state machine that controlled the color of an RGB LED. Spa gta 5. Thestate machine was programmed to light up the RGB LED in a specificsequence of colors.

The state machine advanced from one color to theother only when the button was pressed.We would like to implement the same example but instead of utilizing apolling approach we will utilize and interrupt approach.i.e. Each timethe button is pressed code execution jumps to an interrupt serviceroutine/handler (ISR). In this handler a flag variable is checked. Themain code will then check this flag variable. If it is set then the RGBLED state machine will advance and the RGB will light up with the nextcolor in the sequence.So lets apply the general procedure posted above to this particularproblem.The STM32F0Discovery button is connected to the PA0 pin. According toFigure 2 the PA0 pin is connected to the EXTI0 external interruptline.

So to map the PA0 pin to the EXTI0 line we need to set theEXTI03:0 bits in the SYSCFGEXTICR1 register to 'x000'. Since themost significant bit is a don't care, we could set these bits to'0000'. Note that the SYSCFGEXTICR1 register is all zeroes onreset. So for this particular scenario this action is strictly notnecessary but would not hurt SYSCFG - EXTICR1 &= ( 0x000F ); //clear bits 3:0 in the SYSCFGEXTICR1 reg.The PA0 button is toa pulldown resistor by default. When the button is pressed, thevoltage on the pin change from GND to VDD i.e. The pin exhibits arising edge.

So we will configure PAo to trigger an interrupt eventon the EXTIo line on a rising edge by setting the '0'th bit in theEXTIRTSR register. EXTI - RTSR = EXTIRTSRTR0;.Unmask the external interrupt line EXTI0. By setting the bitcorresponding to the EXTI0 'bit 0' in the EXTIMR register. EXTI - RTSR = EXTIIMRMR0;.The next step is to set the priority for the interrupt. Eachinterrupt in Figure 1 can be set a priority between 0(highestpriority)-3(lowest priority).

These priority settings help manage thenesting of interrupts and is important in improving theresponsiveness of an embedded system. For example If an interruptsubroutine for a low priority interrupt is running when a higherpriority interrupt event occurs, code execution will switch from thelower priority ISR to the higher priority ISR. Once the higherpriority ISR completes, code execution will then return to the lowerpriority ISR. Once that ISR completes, code execution returns to the'main' function.

Well what if two interrupts of the same priorityhappen at the same time? In that case the one with the smallerposition/vector number (placed higher up in Figure 1) will run firstand the other will be put in a pending state. Once the ISR for thefirst interrupt completes, code execution switches to the ISR of thesecond interrupt. This is sometimes referred to as a 'naturalpriority scheme'. The NVIC contains 8 32-bit registersNVICIPR0-NVICIPR7.

The value of the 2 most significant bits ofeach byte in each of these registers control determines the priorityfor a specific interrupt in the table in Figure 1. The CMSIS librarycontains a function that makes this job much easier. It's called'NVICSetPriority'. This function takes two parameters; the firstone is the position/vector number of the interrupt of interest.

Inour case the position number of the EXTI0 interrupt is 5. The secondone is the priority for that interrupt source which can be set from0(highest) to 3(lowest).

We will choose to set it to one just forfun. If you look inside your 'stm32f0xx.h' file you'll find that thelabel 'EXTI01IRQn' is defined as 5. NVICSetPriority ( EXTI01IRQn, 1 ); // alternatively NVICSetPriority(5,1).The next step is to enable the interrupt in the NVIC (Note that itsvery important to set the interrupt priority before you enable theinterrupt). One can do this by setting bit 5 of the NVICISERregister. Or alternatively use the CMSIS function 'NVICEnableIRQ'which takes the interrupt source position in the table in Figure 1 asa parameter.

In our case that's 'EXTI01IRQn' or 5. NVICEnableIRQ ( EXTI01IRQn );.The next step is to write the interrupt service routine (ISR).